高効率・低ノイズ化を実現するGaNデバイス駆動技術

- パワーエレクトロニクス

- ワイドギャップ半導体

- ゲートドライブ回路

- スパイクゲート電圧

- 高効率

近年、電力変換器の高電力密度化実現のためにGaN GIT(窒化ガリウム、ゲート注入トランジスタ)を使用した高速スイッチング回路が注目されている。GaN GITは超高速スイッチング性能を備えているが、閾値電圧が低いために誤点弧を引き起こす可能性がある。誤点弧現象を防ぐために、従来はRC型ゲート駆動法が使用されている。ただし、ターンオフ期間中に過大なスパイクゲート電圧が発生するため、ターンオフのスピードを遅くする必要があり、GaN本来の高速性を活かし切れていなかった。この問題を解決するために、本稿では2段階ターンオフ方式を使用したGaN GIT向けゲート駆動回路を提案する。低スパイクゲート電圧と高速ターンオフスイッチングの相反する性能を同時に満たすことが可能である。この回路は、GaN GITを使用してボードに実装され、同期整流型DC/DCコンバータに適用し、実験的に有用性を確認出来た。

1. まえがき

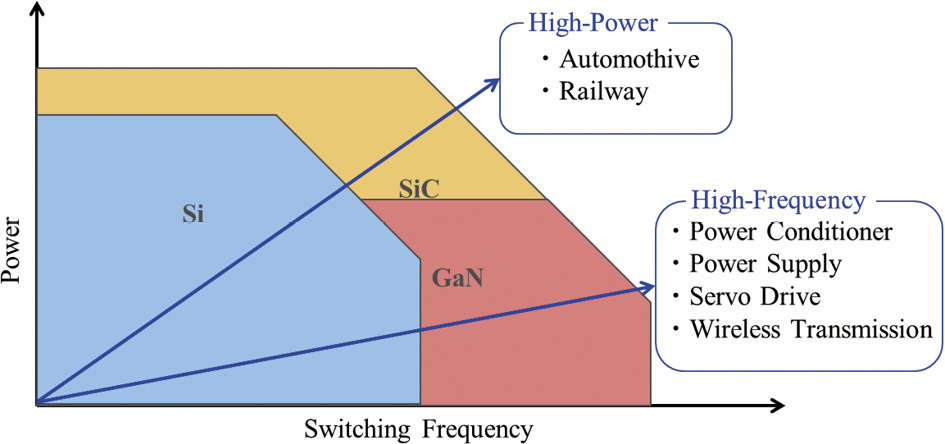

近年、電力変換器の高電力密度、高効率化実現に向けて、シリコン(Si)に代わる新しい半導体デバイスの材料として、ワイドギャップ半導体が注目されている1)。電力変換器は冷却部品(ヒートシンク)、受動部品(コンデンサ、リアクトル)が大きな割合を占めており、高効率化・高周波化によりこれらの小型化・低コスト化を実現出来る。オムロンの製品群である電力変換器(パワーコンディショナ、汎用電源、サーボドライブ)は数百 W~数kW程度であり、図1に示すように特に窒化ガリウム(GaN)の適用を検討している。Siデバイスは大きな入力、及び出力容量を持ち、またボディダイオードの逆回復動作が悪いのに対し、GaNデバイスはこれらの容量がはるかに小さく、逆回復特性が優れている。従って、GaNデバイスを使用することで高効率を実現できる。GaNデバイスの物性特性を限界まで引き出すために、垂直型構造2)、横型構造3)など、様々な内部構造を持つGaNデバイスが開発されている。デプレッションモード4)GaNはノーマリーオンデバイスであり、エンハンスメントモード(E-M)5)GaNは扱いやすいノーマリーオフを実現している。またMOSFETを使用したハイブリッドモード(H-M)6)構造も開発されている。表1に入手可能な代表的なデバイスのパラメータ比較を示す。なお青字は利点、赤字は欠点を示す。GaN GIT(ゲート注入トランジスタ)7)は、ノーマリーオフ動作と表1の通り容量C、電荷量Q が小さく高速駆動を実現できるデバイスとして注目されている。

| Si | SiC | GaN H-M |

GaN E-M |

GaN GIT |

|

|---|---|---|---|---|---|

| Vds [V] | 600 | 650 | 650 | 650 | 600 |

| Id [A] Max. | 35 | 39 | 34 | 30 | 31 |

| Rdson [mΩ] Typ. | 52 | 48 | 50 | 50 | 55 |

| Ciss [pF] Typ. | 2850 | 1118 | 1000 | 242 | 380 |

| Co (tr) [pF] Typ. | 1050 | 194 | 310 | 160 | 102 |

| Qg [nC] Typ. | 68 | 33 | 16 | 6.1 | 5.8 |

| Qoss [nC] Typ. | ― | 78 | 126 | 64 | 41 |

| Qrr [nC] Typ. | 6000 | 125 | 126 | 0 | 0 |

| Vth [V] Typ. | 3.5 | 4.5 | 4 | 1.7 | 1.2 |

本論文では、GaN GITに焦点を絞り説明する。このデバイスの閾値電圧Vthは、表1の通りSiデバイスよりもはるかに低く、オフ状態の維持はGaN GITにとって非常に重要である。GaN GITはノイズに敏感であり、負のゲート電圧は、ミラー電流によるGaN GITの誤点弧防止に必要である。負のゲート電圧がないために、誤点弧が発生した場合、アーム短絡現象が発生し、壊滅的な障害につながる可能性がある。負のゲート電圧は通常、バイポーラ電源で実装される。GaN GITのスイッチング性能を引き出すためにはRC型ゲート駆動法8,9,10,11)が提案されている。この方法により、GaN GITのゲートをより高い電圧で駆動できるため、スイッチングが高速にできる。ただし、ターンオフの高速性故に大きな負のスパイクゲート電圧が発生する。

これらの問題を解決するために、低ノイズと高速ターンオフスイッチングの相反する性能を同時に実現可能なGaN GITゲート駆動法「2段階ターンオフ方式」を提案する。2章、3章では従来のゲート駆動回路、及び提案するゲート駆動回路の動作原理について説明する。4章では、提案するゲート駆動回路を同期整流型DC/DCコンバータに適用し、有効性を実験により確認した。

2. 従来のゲート駆動回路

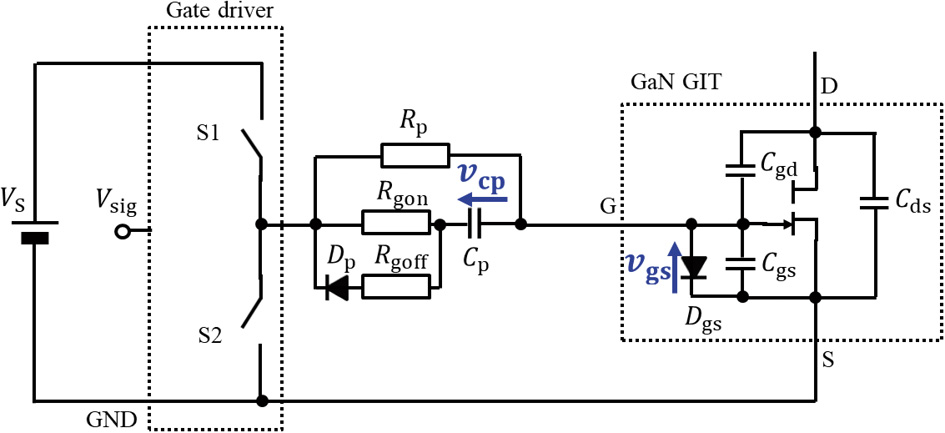

2.1 回路構成

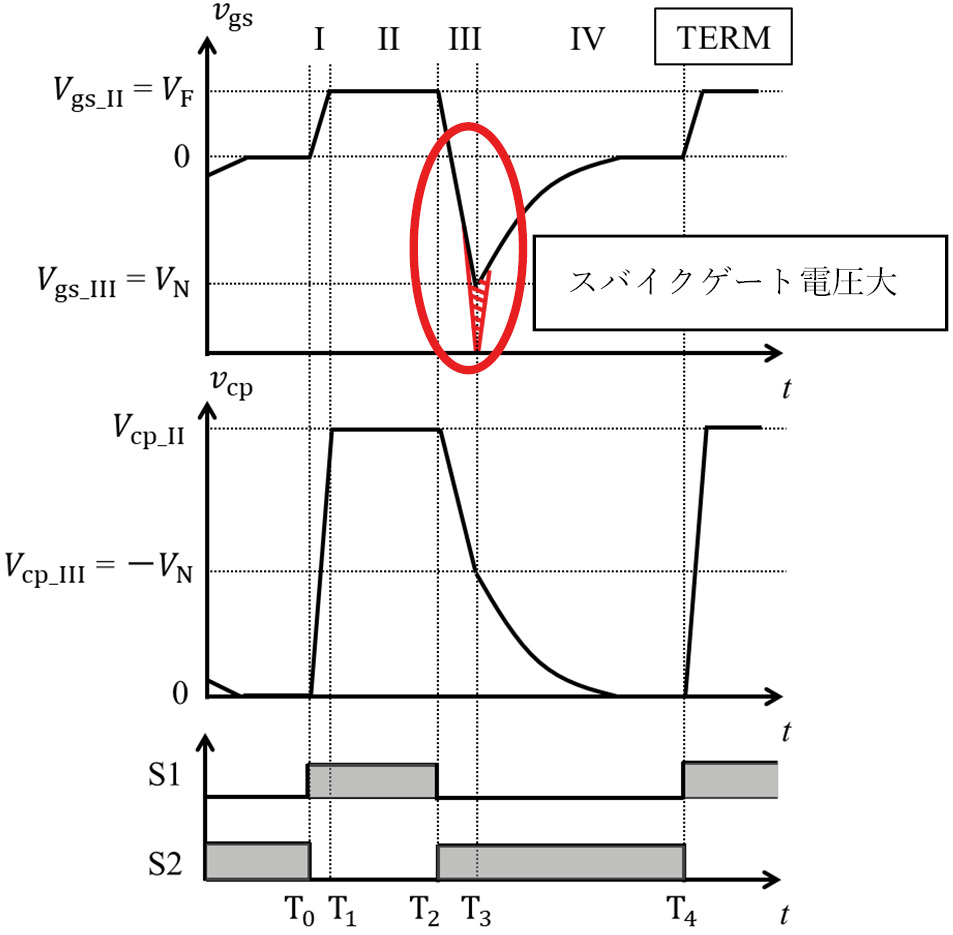

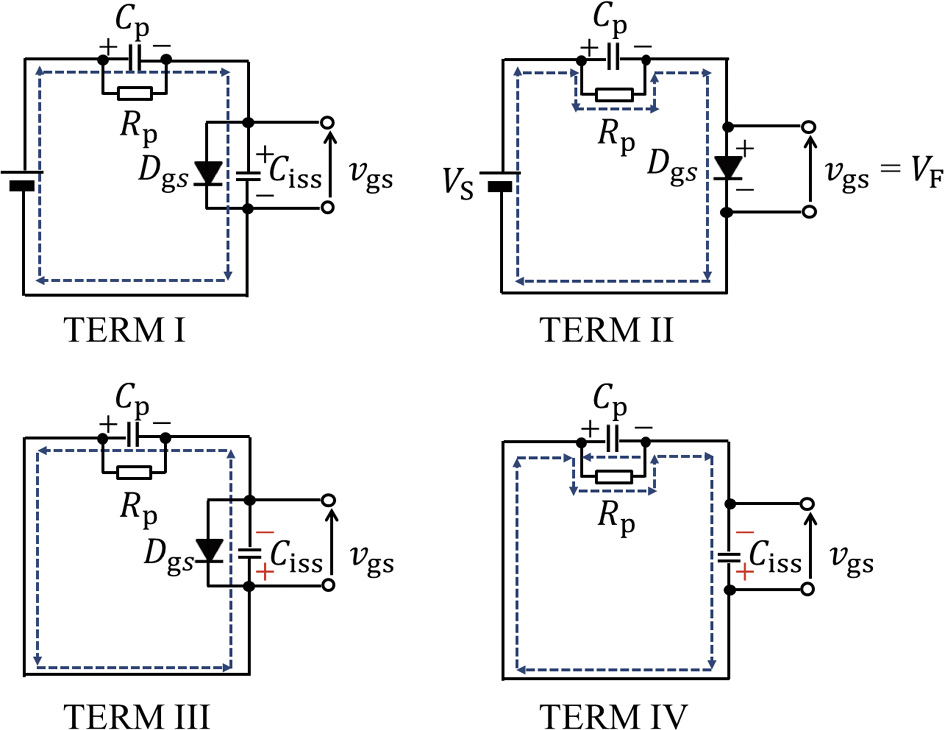

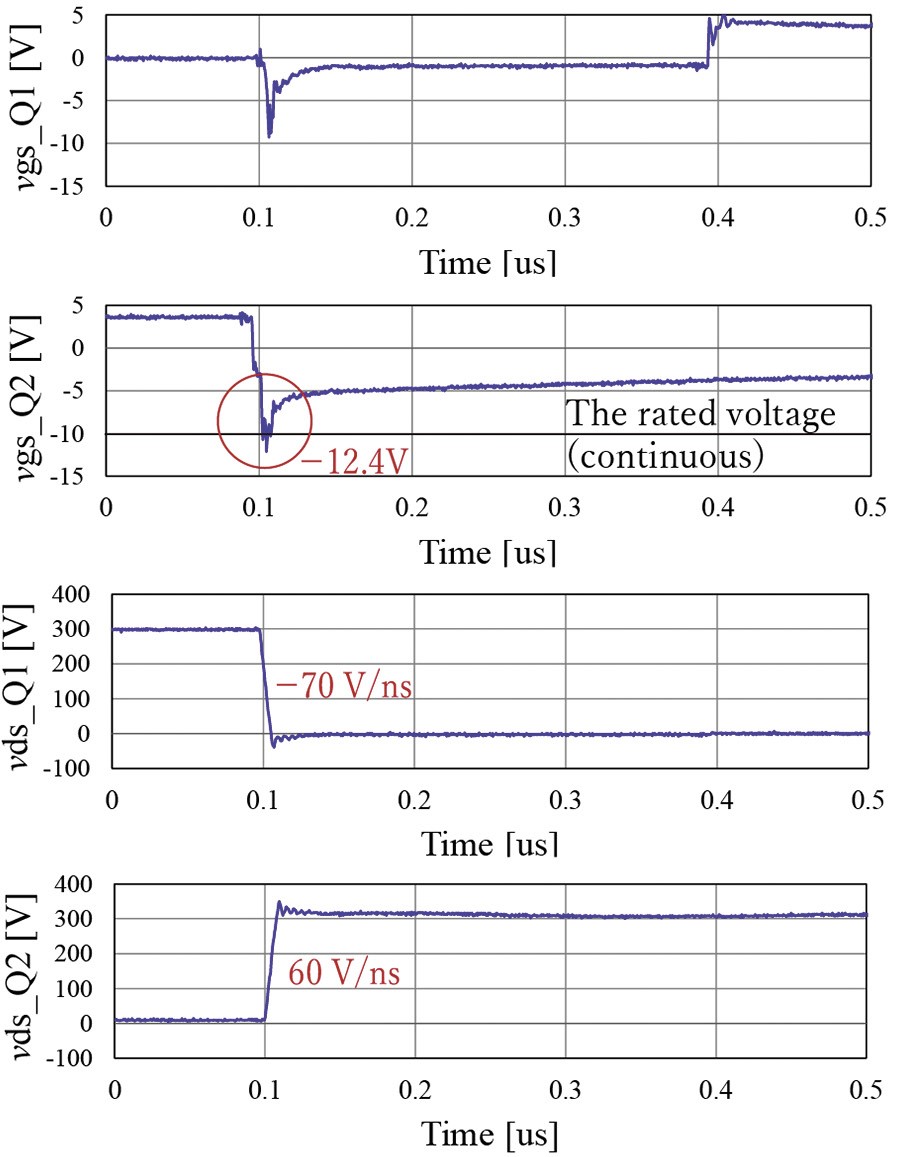

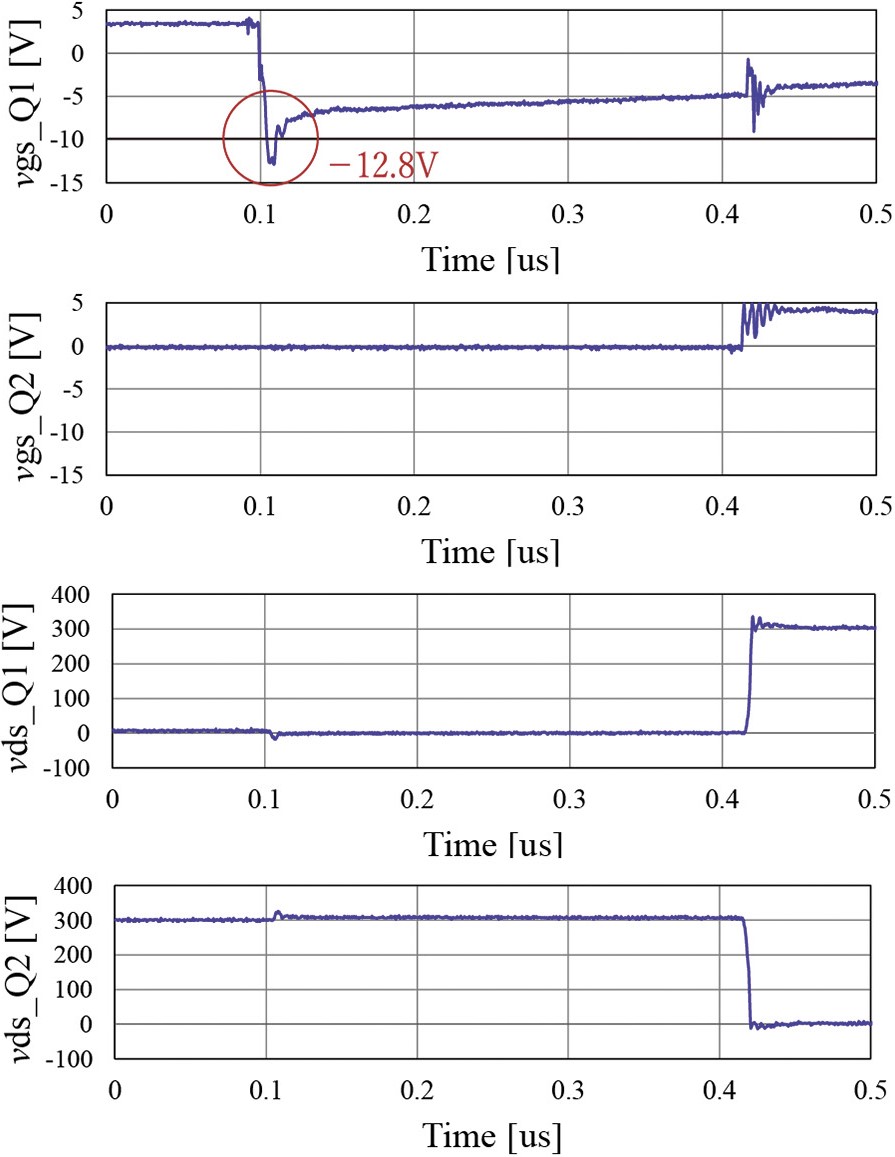

図2に従来のRC型ゲート駆動回路構成を示す。この回路はシンプル、かつ長年の実績があるが図3(赤い丸で囲んだ部分)に示すように、より速いターンオフ中に大きな負のスパイクゲート電圧を引き起こす可能性がある。従って、高周波スイッチングを阻害してしまう。

2.2 動作原理

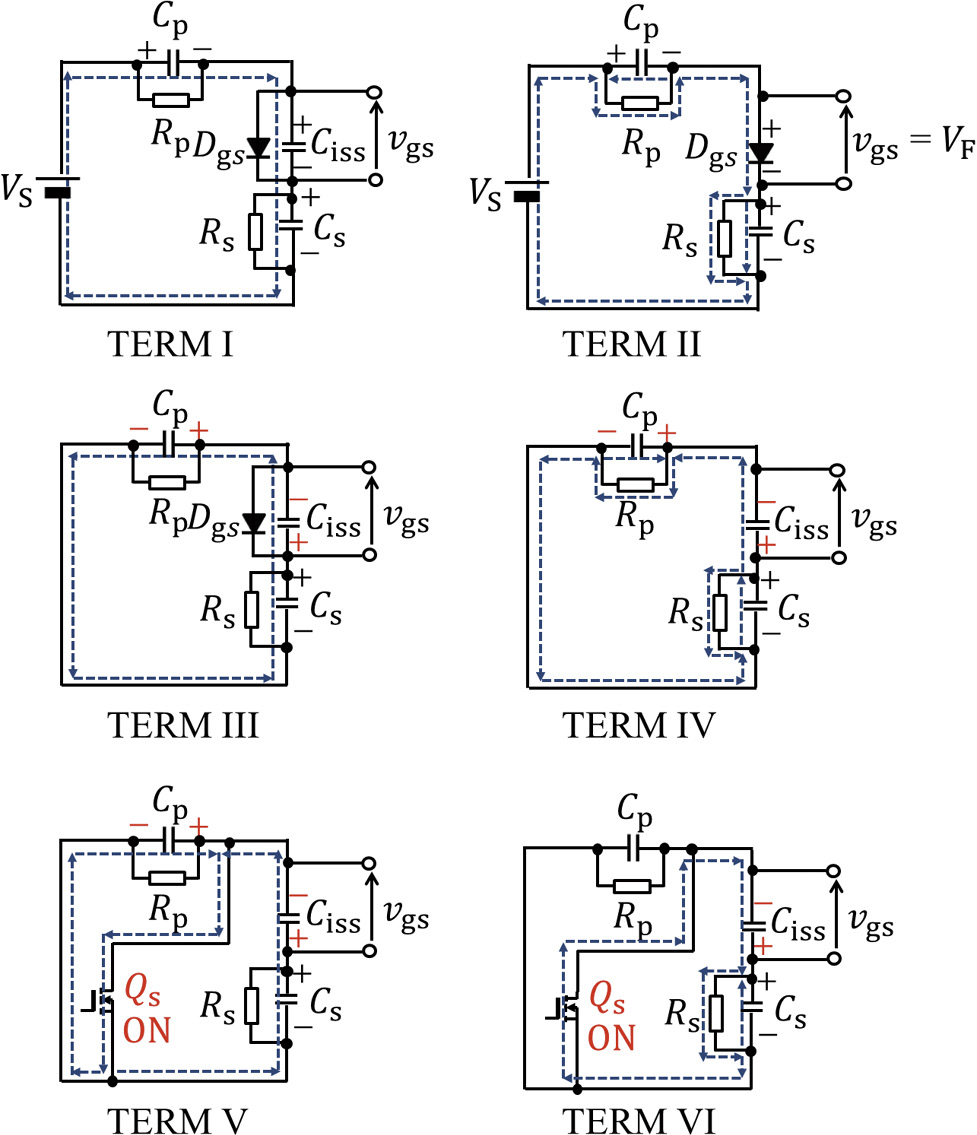

図3に動作シーケンスを示す。図4に、従来のRC型ゲート駆動回路の各期間での等価回路を示す。図3に関して、RgonとRgoffは非常に小さいため、無視して動作原理を説明する。

TERM Ⅰ [

T0でスイッチS1がオンになると、GaN GITの入力容量(Ciss=Cgs+Cgd)は容量CPを介して充電を開始する。同時に、GaN GITのゲートとソースの間に形成された寄生ダイオードDgsに電流が流れ始める。

TERM Ⅱ [

ターンオンが完了すると、ゲート電流は常にRPを通ってゲートとソースの間の寄生ダイオードに流れ、ターンオン状態を維持する。vgsは、寄生ダイオードの順方向電圧(VF)でクランプされる。これは、GaN GITのバンドギャップによって決まる。RPは、一般に寄生ダイオードのVFが約3.5 Vになるように設計される。期間Ⅱのvgs_IIおよびVCP_II電圧は、式(1)および式(2)で与えられる。ここで、VSはゲート供給電圧である。

TERM Ⅲ [

T2でスイッチS2がオンになると、CissはCPを介して放電を開始する。vgsはそれに応じて減少する。負電圧VNは、一般的なMOSFETの式(3)12)を使用して計算可能である。ここで、Qg は0 VからVFまでの総ゲート電荷量である。スイッチング速度はRgoffによって調整可能である。ゲート電圧が急峻に負電圧に変化するため、VNに追加で大きなスパイクゲート電圧が発生する。

TERM Ⅳ [

CissとCPは、RPを介して放電される。ゲート電圧vgsは、上記のRC時定数で0 Vに近づく。期間IV中のvgs_IV電圧は式(4)で与えられる。

![vgs_Ⅳ(t)=VN・exp[-(t-T3)/RP(CP+Ciss)]](/jp/ja/assets/img/technology/omrontechnics/20210510/20210510-053-015-math-04.svg)

3.提案のゲート駆動回路

3.1 回路構成

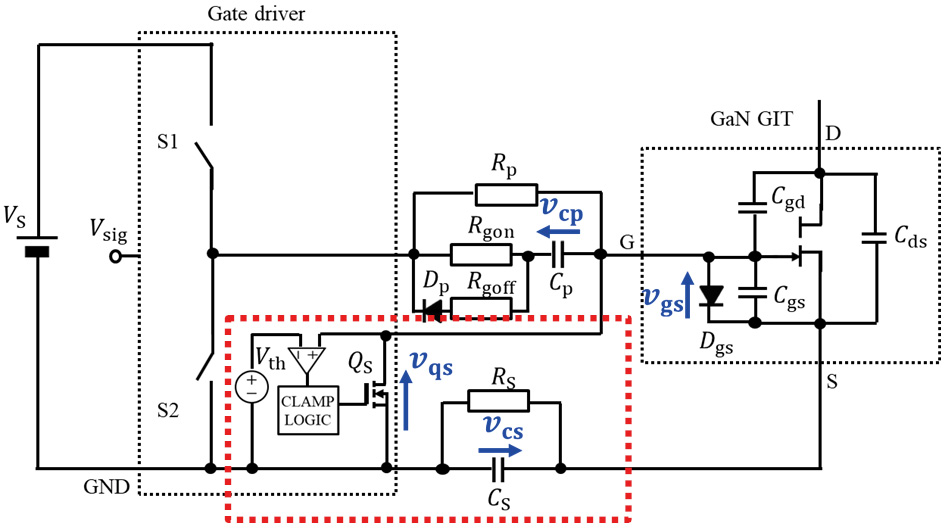

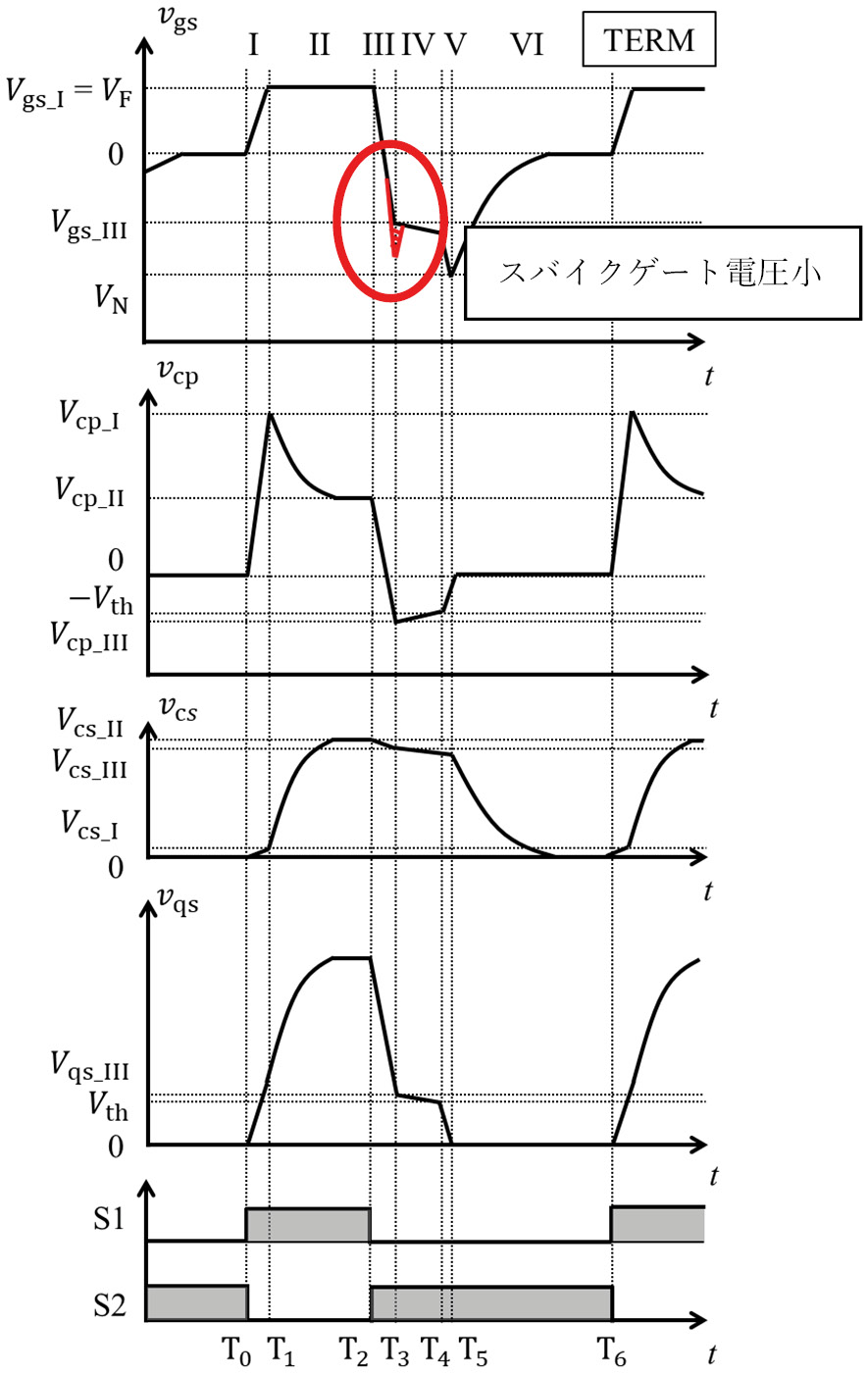

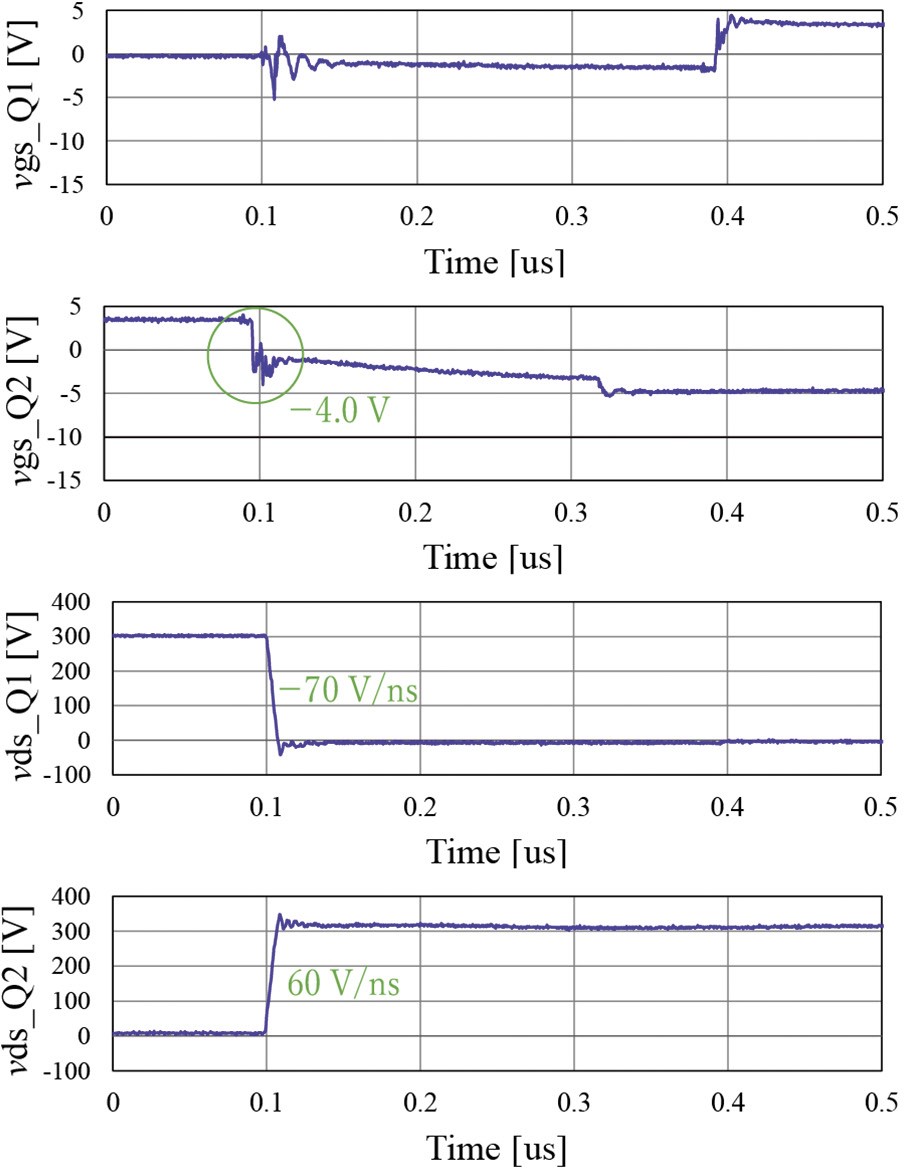

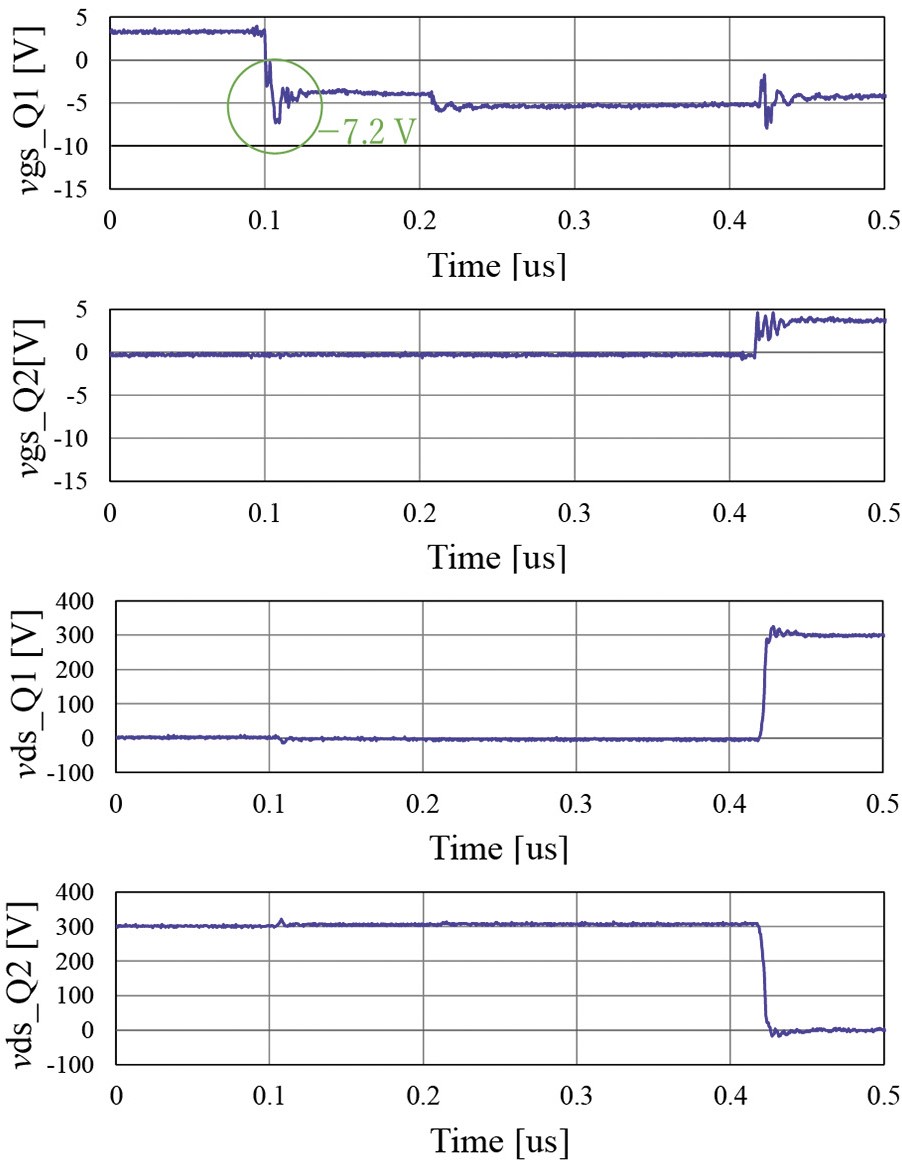

図5に、QS、RS、CS(赤い破線部分)で構成される「2段階ターンオフ」のゲート駆動回路を示す。ミラー電流によって引き起こされるパワートランジスタの誤ったターンオンを防ぐために使用されるアクティブミラークランプMOSFET QS は、市販のゲートドライバで実装されている。 ミラークランプ機能を使用すると、パワートランジスタのゲート電圧は通常、オフ状態のときに約2 V未満でクランプされる。提案したゲート駆動回路は、図6(赤い丸で囲んだ部分)に示すように、ターンオフ中のスパイクゲート電圧を低減可能である。

3.2 動作原理

図6に動作シーケンスを示す。図7に、提案したゲート駆動回路の各期間で等価回路を示す。図7に関して、Rgon、Rgoff、およびMOSFET QS の静電容量はCPおよびCSより非常に小さいため無視する。

TERM Ⅰ [

T0でスイッチS1がオンになると、GaN GITの入力容量(Ciss)は、CPおよびCSを介して充電を開始する。期間Iの終了時のVgs_I、VCP_I、およびVCS_I電圧は、式(5)、式(6)、および式(7)に示される。

TERM Ⅱ [

T1でターンオンが完了すると、vgsは寄生ダイオードDgsの順方向電圧(VF)でクランプされる。CPとCSは、RPとRSを介して放電および充電される。期間IIの終了時のVCP_IIおよびVCS_II電圧は、MOSFETの一般式12)により式(8)、式(9)で表される。

![VCP_Ⅱ=VCP_Ⅰ(1-CP+CS/CS RP/RP+RS)・exp[-(T2-T1)/(RP・RS/RP+RS)(CP+CS)]+(VS-VF)RP/RP+RS](/jp/ja/assets/img/technology/omrontechnics/20210510/20210510-053-015-math-08.svg)

![VCS_Ⅱ=VCS_Ⅰ(CP+CS/CP RS/RP+RS-1)[1-exp[-(T2-T1)/(RP・RS/RP+RS)(CP+CS)]]+VCS_Ⅰ](/jp/ja/assets/img/technology/omrontechnics/20210510/20210510-053-015-math-09.svg)

TERM Ⅲ [

T2でスイッチS2がオンになると、GaN GITのCissは、CPおよびCSを介して放電を開始する。 各々のコンデンサの電荷が均衡すると、放電は終了する。 期間Ⅲの終了時のVgs_III、VCP_III、VCS_III、およびVqs電圧は、式(10)から式(13)に示す。これらは、電荷保存則を適用して導出される。2段階ターンオフを実現するには、Vqs_IIIをスレッショルド電圧(Vth)より高い値でクランプする必要がある。 その結果、スパイクゲート電圧は従来のRC型回路に比べて低減する(図6)。

![Vgs_Ⅲ=CP[Qg-VCS_Ⅱ・CS]+CS[Qg-VCP_Ⅱ・CP]/(CP・CS+CS・Ciss+Ciss・CP)](/jp/ja/assets/img/technology/omrontechnics/20210510/20210510-053-015-math-10.svg)

![VCP_Ⅲ=CS[VCP_Ⅱ・CP-Qg]+Ciss[VCP_Ⅱ・CP-VCS_Ⅱ・CS]/(CP・CS+CS・Ciss+Ciss・CP)](/jp/ja/assets/img/technology/omrontechnics/20210510/20210510-053-015-math-11.svg)

![VCS_Ⅲ=CP[VCS_Ⅱ・CS-Qg]+Ciss[VCS_Ⅱ・CS-VCP_Ⅱ・CP]/(CP・CS+CS・Ciss+Ciss・CP)](/jp/ja/assets/img/technology/omrontechnics/20210510/20210510-053-015-math-12.svg)

TERM Ⅳ [

Ciss、CP、およびCSは、RPおよびRSを介して放電される。

TERM Ⅴ [

ゲート端子とゲート電源GND端子間の電圧vqsがスレッショルド電圧(Vth)より低くなると、MOSFET QS がONする。同時に、Ciss、CP、およびCSは、MOSFET QS の経路で瞬時に放電される。

TERM Ⅵ [

CissとCSは、RSを介して放電される。ゲート電圧vgsは、上記のRC時定数で0 Vに近づく。

4. 実験結果

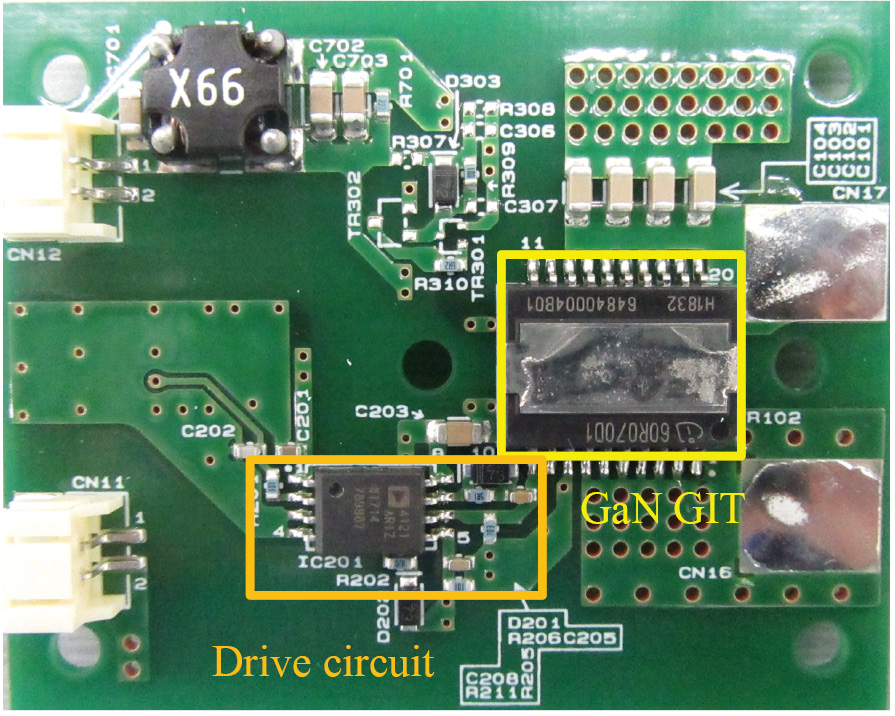

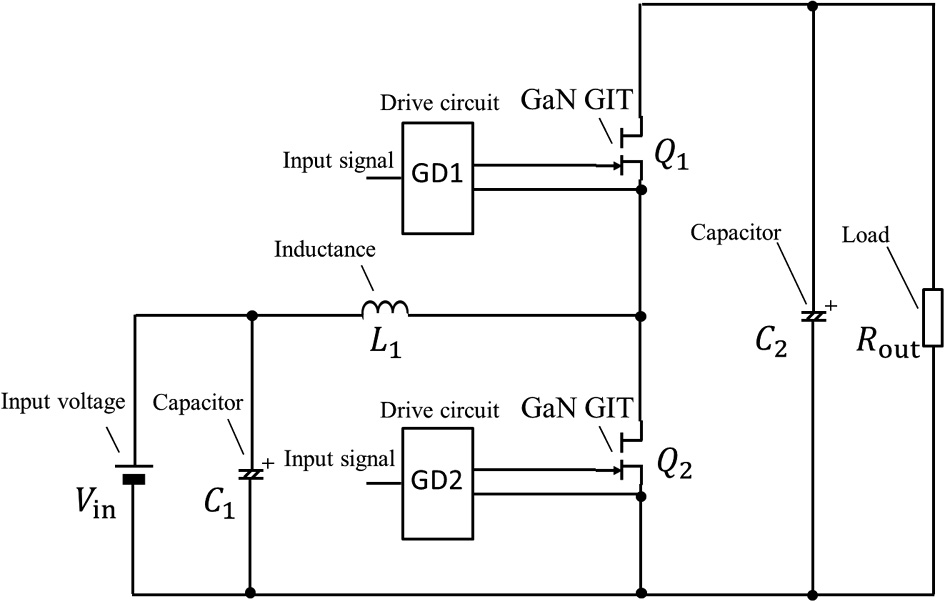

図8と図9に、使用した評価ボードと同期整流型DC/DCコンバータのブロック図を示す。従来回路と提案回路をゲート駆動回路(GD1、GD2)に適用し、GaN GITはIGOT60R070D1(Infineon)13)を使用した。デバイスの定格動作領域を考慮しVin=150 V、Vout=300 V、Pout=0.25- 1 kW、fSW=20 kHzの昇圧動作条件で評価を行った。表2に、使用したパラメータを示す。CPは、ミラー電流によって引き起こされるGaN GITの誤ったターンオンを防ぐために、約VN=-5.0 Vに調整した。

| 構成部品 | 定数 | |

|---|---|---|

| 従来回路 | 提案回路 | |

| Rp | 330 Ω | 130 Ω |

| Rs | ― | 200 Ω |

| Rgon | 22 Ω | 22 Ω |

| Rgoff | 0 Ω | 0 Ω |

| Cp | 3.2 nF | 1.0 nF |

| Cs | ― | 22 nF |

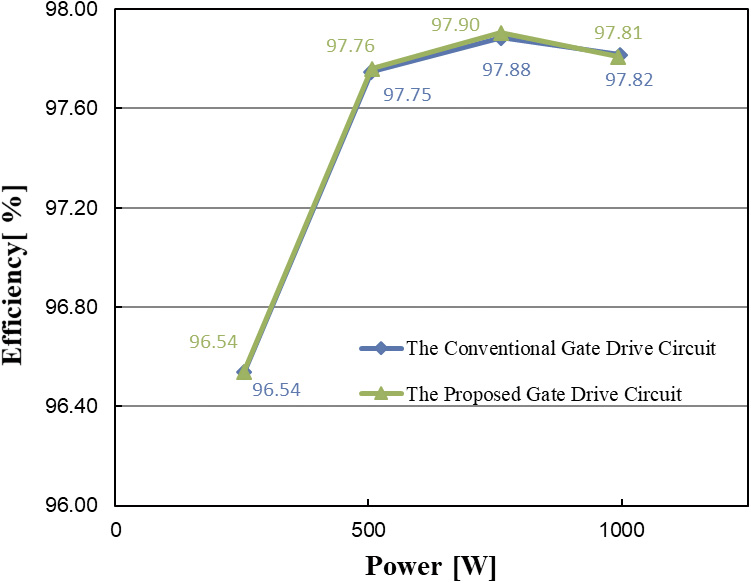

図10に効率測定結果を示す。従来回路と提案回路で効率に差がないことがわかる。図11に、Pout=1 kW条件における従来のゲート駆動回路波形(図11(a))と提案したゲート駆動回路波形(図11(b))を示す。左欄はQ2 デバイスがターンオフ時、右欄はQ1 デバイスがターンオフ時の波形である。電圧信号vgsおよびvdsは、光アイソレーション差動プローブ(TIVM1、TIVH08:Tektronix社製)によって検出した。デバイスQ1 のターンオフ時のスパイクゲート電圧は、従来回路では-12.8 V、提案回路では-7.2 Vである。提案回路は、従来のものと比較して、スパイクゲート電圧を5.6 V改善した。同様に、デバイスQ2 のターンオフ時のスパイクゲート電圧は、従来回路では-12.4 V、提案回路では-4.0 Vである。提案回路は、従来のものと比較して、スパイクゲート電圧を8.4 V改善した。提案駆動回路は、デバイスQ1、Q2 のターンオフ時において、ともに2段階ターンオフスイッチングを実現できているため、スパイクゲート電圧の発生を抑制している。従って、-10 Vの定格ゲート-ソース間電圧に対して十分なマージンを確保できる。また、従来の回路との間で、Q1 と Q2 のターンオフ時のドレイン-ソース間電圧のスイッチング速度に大きな相違はない。さらに提案回路は、スイッチング期間中にゲート電圧に重畳されるミラーノイズが低減可能であり、スイッチング期間中にミラークランプMOSFET QS によりゲート回路の低インピーダンスを実現できると考えられる。これらの結果から、2段階ターンオフ回路を適用することにより、低スパイクゲート電圧と高速ターンオフスイッチングの相反する性能を同時に満たすことが実験により確認出来た。

Q2 ターンオフ時

Q2 ターンオフ時 Q1 ターンオフ時

Q1 ターンオフ時

Q2 ターンオフ時

Q2 ターンオフ時 Q1 ターンオフ時

Q1 ターンオフ時

5. むすび

従来のゲート駆動回路では、スイッチング時に大きなスパイクゲート電圧が発生し、高速スイッチング・高効率化を阻害する課題があった。そこで本論文では、低ノイズと高速ターンオフスイッチングの相反する性能を同時に実現できる、GaN GITゲート駆動のための「2段階ターンオフ方式」を提案した。提案したゲート駆動回路を用いて同期整流型DC/DCコンバータに実装し、実機評価した。高速ターンオフスイッチング特性、及び効率を損なうことなく、スパイクゲート電圧が最大8.4 V低下することが確認され、-10 Vの定格ゲート-ソース間電圧に対して十分なマージンを確保でき、本方式の有効性を示した。

今後は、駆動条件に合わせた回路定数の最適化を検討していく。

参考文献

- 1)

- Jones, E. A.; Wang, F. F.; Costinett, D. Review of Commercial GaN Power Devices and GaN-Based Converter Design Challenges. IEEE Journal of Emerging and Selected Topics in Power Electronics. September 2016, Vol.4, Issue 3, p.707-719.

- 2)

- Oka, T.; Ina, T.; Ueno, Y.; Nishii, J. Over 10 A Operation with Switching Characteristics of 1.2 kV-Class Vertical GaN Trench MOSFETs on a Bulk GaN Substrate. Proc. 28th Int. Symp. Power Semiconductor Devices and IC’s. July 2016, p.459-462.

- 3)

- Hilt, O.; Treidel, E.; Wolf, M.; Kuring, C.; Tetzner, K.; Yazdani, H.; Wentzel, A.; Würfl, J. Lateral and vertical power transistors in GaN and Ga2O3. IET Power Electron. December 2019, Vol.12 Issue 15, p.3919-3927.

- 4)

- Hahn, H.; Reuters, B.; Pooth, A.; Holländer, B.; Heuken, M.; Kalisch, H.; Vescan, A. p-Channel Enhancement and Depletion Mode GaN-Based HFETs With Quaternary Backbarriers. IEEE Transactions on Electron Devices. October 2013, Vol.60, No.10, p.3005-3011.

- 5)

- Cai, Y.; Zhou, Y.; Chen, K.; Lau, K. High-Performance Enhancement-Mode AlGaN/GaN HEMTs Using Fluoride-Based Plasma Treatment”. IEEE Electron Device Letters. July 2005, Vol.26, No.7, p.435-437.

- 6)

- Huang, X.; Liu, Z.; Li, Q.; Lee, F. C. Evaluation and Application of 600 V GaN HEMT in Cascode Structure. IEEE Transactions Power Electon. May 2014, Vol.29, No.5, p.2453-2461.

- 7)

- Uemoto, Y.; Hikita, M.; Ueno, H.; Matsuo, H.; Ishida, H.; Yanagihara, M.; Ueda, T.; Tanaka, T.; Ueda, D. Gate Injection Transistor (GIT)- A Normally-Off AlGaN/GaN Power Transistor Using Conductivity Modulation. IEEE Transactions Electron Devices. November 2007, Vol.54, No.12, p.3393-3399.

- 8)

- Morita, T.; Handa, H.; Ujita, S.; Ishida, M.; Ueda, T. 99.3% Efficiency of Boost-Up Converter for Totem-Pole Bridgeless PFC Using GaN Gate Injection Transistor. Proceedings of the International Exhibition and Conference for Power Electronics, Intelligent Motion, Renewable Energy and Energy Management, PCIM Europe. May 2014, p.325-329.

- 9)

- Li, H.; Han, C.; Brothers, J.; Zhang, X.; Wang, J. Evaluation of 600 V GaN based gate injection transistors for high temperature and high efficiency applications. 2015 IEEE 3rd Workshop on Wide Bandgap Power Devices and Applications (WiPDA). November 2015, p.85-91.

- 10)

- Abdullah, Y.; Li, H.; Wang, J. Evaluation of 600 V Direct-Drive GaN HEMT and a Comparison to GaN GIT. IEEE 5th Workshop on Wide Bandgap Power Devices and Applications (WiPDA). November 2017, p.273-276.

- 11)

- Bortis, D.; Knecht, O.; Neumayr, D.; Kolar, J. W. Comprehensive Evaluation of GaN GIT in Low- and High-Frequency Bridge Leg Applications. 2016 IEEE 8th international Power Electronics and Motion Control Conference (IPEMC-ECCE Asia). May 2016, p.21-30.

- 12)

- Zojer, B. 600 V CoolGaN™ high electron mobility transistors. AN_201702_PL52_012, Infineon Technologies AG, 2018.

- 13)

- Infineon Technologies AG. “IGOT60R070D1, 600V CoolGaN™ enhancement-mode power transistor”. datasheet, 2020.

本文に掲載の商品の名称は、各社が商標としている場合があります。